# EMD1 de Structure Machine (2006/2007)

Durée : 2 heures Documents non autorisés

## Exercice 1 (4 points).

- a. / Définissez brièvement la représentation des nombres réels : (Signe et valeur absolue, complément à 1, complément vrai).

- **b.** / on considère un nombre en virgule flottante représentée sur une machine ayant les caractéristiques suivantes : 1bit de signe, 3 bit d'exposant décalé (biaisé) et de 3 bits pour la mantisse normalisée.

Questions: 1. Quel est le biais

- 2. Représenter sur cette machine les nombre suivant : (5.625)10 et (5)10

- 3. Que remarquez vous?

### Exercice 2 ( 4 points).

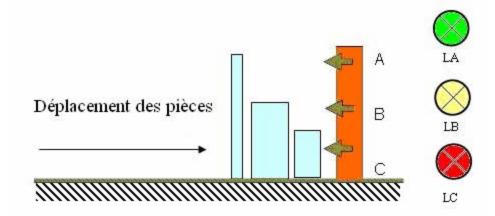

Le circuit suivant permet de trier des pièces selon leur taille. Le circuit est constitué de trois capteurs A, B, C.

Fonctionnement: Les pièces se déplacent sur un tapis et suivant leur taille, leur détection permet l'allumage d'une des trois lampes:

LA (pièce de grande taille), LB (pièce de taille moyenne), LC (pièce de petite taille).

### Questions:

Etudier le circuit le circuit et donner les équations des différentes lampes (Table de vérité, simplification par karnaugh, équations logiques).

Exemple: si une pièce est de taille moyenne, alors elle est détectée par B et C, mais seul la lampe LB est allumée.

# Exercice 3 (6 points).

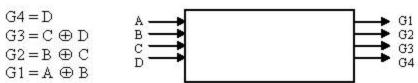

La figure suivante représente le schéma bloc d'un circuit combinatoire ayant :

En Entrées : D, C, B, A (avec A poids faible) dans le système binaire et En Sorties : G4, G3, G2, G1 (avec G1 poids faible). Définies comme suit :

## Questions:

a. / Donner la table de vérité correspondant au circuit

b. / En déduire A, B, C, D en fonction de G1, G2, G3, G4

c. / Que fait ce circuit?

## Exercice 4 (6 points).

Pour effectuer la **Comparaison** de deux nombres A (4bits : A3, A2, A1, A0) et B (4bits : B3, B2, B1, B0), on utilise un **Additionneur** de 4bits et des portes logiques de façon à obtenir trois sorties :

$$X = 1 \text{ si } A > B$$

;  $Y = 1 \text{ si } A = B$ ;  $Z = 1 \text{ si } A < B$

## Questions

a./ Compléter le tableau suivant avec :

La somme S  $(S_3, S_2, S_1, S_0) = A + CV(B)$  CV : Complément Vrai (à 2)

La somme logique : SL = (S3 + S2 + S1 + S0)

R: Retenue finale de l'addition

|           | Exemples    | R | Somme<br>S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | SL | X | Y | Z |

|-----------|-------------|---|----------------------------------------------------------------------|----|---|---|---|

| A > B     | A=5; $B=2$  |   |                                                                      |    |   |   |   |

| A = B     | A= 2; B = 2 |   |                                                                      |    |   |   |   |

| $A \le B$ | A= 2; B = 5 |   |                                                                      |    |   |   |   |

- b. / Donner les équations de X, Y, Z en fonction uniquement de R et SL

- c. / Faire le schéma du Comparateur en utilisant un additionneur 4 bits et un minimum de portes logiques.

- **d.** / Donner le schéma global qui permet de donner le **Minimum** des deux nombres A et B de 4 bits chacun tel que :

$$Min = A si (A \le B);$$

$$Min = B si (A \ge B).$$

Remarque : pour le schéma, utiliser le circuit trouvé précédemment et un minimum de circuits combinatoires jugés nécessaires.

Bon Courage -

Enseignants : Balla- Chérid- Zemirli